|

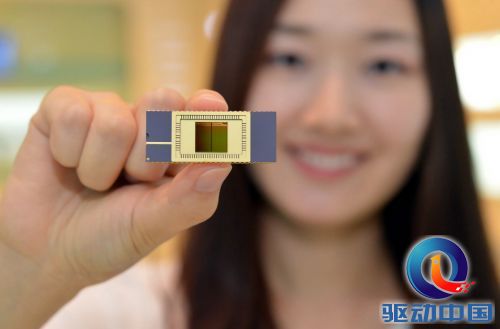

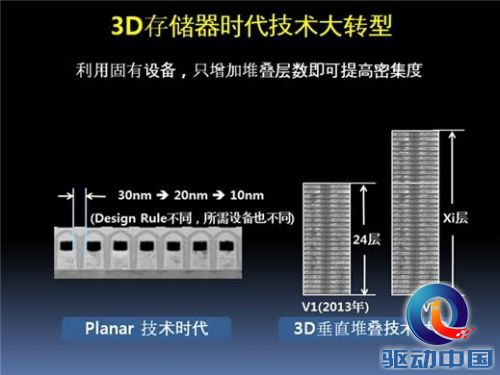

◇已达到微细化和大容量化极限的内存技术开拓新纪元 - 新概念3D垂直堆叠,开发出“结构+制程”双创新 - 凭借10年来300余项核心专利技术,全球最先成功实现产品商业化 ◇高密度3D垂直型堆叠结构,同时实现性能和可靠性的提高 - 相比单层结构,创新的3D结构使密度提高两倍以上 - 写入速度提高两倍,存储单元使用寿命最大增加十倍 ◇确保引领今后Tb级大容量闪存芯片量产技术 - 以超越极限的NAND闪存新技术保证市场持续增长 - 三星以充分的3D存储器核心技术确保绝对竞争优势 三星电子开创了内存芯片的3D时代。三星电子近日表示,从本月6日起在全球最先开始量产突破半导体微细化技术极限的新概念3D垂直堆叠型结构NAND闪存芯片(3D Vertical NAND, 3D V-NAND)。 此次推出的3D垂直堆叠型结构NAND闪存芯片规格为128Gb,为业界最大容量。该产品同时采用了三星独创的“3D圆柱形电荷捕获型栅极存储单元结构技术(3D Charge Trap Flash)”和“3D垂直堆叠制程技术”,与采用20纳米级单层结构的高性能NAND闪存产品相比,密度提高了两倍以上,由此显著提高了生产效率。

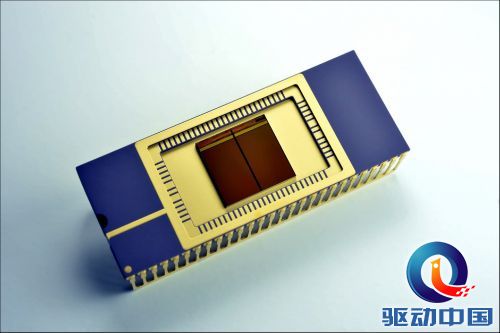

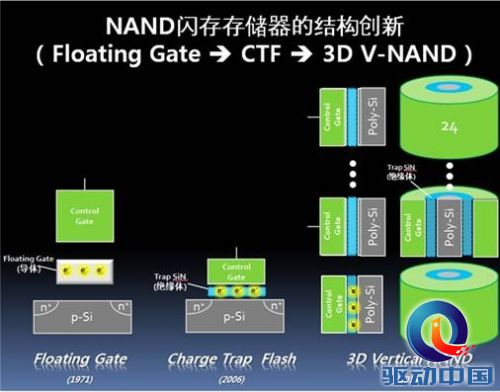

到目前为止,投入量产的闪存芯片采用的是40多年前开发的浮栅(Floating Gate)结构,其原理是将电荷储存于导体。随着近来10纳米级制程工艺开始投入使用,存储单元间的间隔大幅缩小,使得电子外漏导致的电子干扰现象越来越严重。可以说,NAND闪存的微细化技术已达到了物理极限。 然而,三星电子此次将原来单层排列的存储单元以3D垂直堆叠方式重新排列,不仅同时实现了“结构创新”和“制程创新”,更将原有问题一并解决,为业界开创了“3D闪存芯片量产新纪元”。 三星电子通过多年研究设计出的“3D圆柱形电荷捕获型栅极存储单元结构技术(3D Charge Trap Flash) ”把存储单元像盖摩天大楼一样垂直堆叠24层,是三星电子在全球领先开发的2D平面电荷捕获型栅极芯片技术(2D CTF)的立体3D进化版。采用该结构的存储单元通过把电荷存储在具有高稳定性的绝缘体中,大幅减少了上下存储单元间的电子干扰现象。新产品的写入速度将提高两倍,作为存储单元寿命衡量标准的可擦写次数随产品种类不同也将提高两倍到十倍不等。 “3D垂直堆叠制程技术”则是实现在尽可能小的芯片上放置尽可能多的组件的技术。三星电子开发了从高层向低层穿孔以连接电极的蚀刻技术,以及将存储单元垂直围绕在各层板面上的门极结构技术等一系列独特并有突破性的工艺技术。 此外,三星电子在过去十年研究"3D垂直堆叠型结构NAND闪存(V-NAND)技术"的过程中,研发了300余项核心专利,并已在韩国,美国和日本等世界各国提出了专利申请。 由此,三星电子成功突破了10纳米级以下半导体技术的极限,为将来推出1Tb以上大容量NAND闪存确保了技术来源,也掀开了NAND闪存技术革新的新篇章。换句话说,今后的技术竞争将不再是利用最新的光刻设备来追求微细化的竞争,而是迎来了通过加高堆叠层数来实现大容量化的彻底的技术转型。 三星电子存储芯片事业部闪存开发部负责人崔定爀专务表示:“过去数年间,公司全体员工为突破半导体技术极限并实现技术革新付出了辛勤劳动。公司今后将持续推出具有更高密度和更优良性能的产品,为世界IT产业的不断发展贡献力量。” 据市场调查机构预测,世界NAND闪存芯片市场将持续增长,从今年的236亿美元增长到2016年的308亿美元。 三星电子在全球首次量产3D垂直堆叠型结构NAND闪存,确保了绝对的产品竞争优势,并将在今后以差别化的独创技术持续加强存储器芯片事业的竞争力。 参考资料 ※NAND闪存 (NAND Flash Memory) 在断电情况之下也能完整保存数据的存储器半导体,主要用于在智能手机中存储音乐,照片和视频等,也可用于取代传统HDD硬盘的固态硬盘SSD中。 ※浮栅结构(Floating Gate) 是NAND闪存中用来存储数据的基本单位存储单元的结构。传统的NAND闪存是由控制栅和浮栅组成,并在以导体制成的浮栅上存储电荷。当微细化发展到10纳米级以下时,存储单元之间的电极干扰将会加重,使得制程的微细化变得很困难。 ※CTF结构(Charge Trap Flash) 仅由控制栅组成,取代传统浮栅的是奶酪状的绝缘体,并在该绝缘体的空隙中存储电荷。由于只有一个栅极,存储单元的高度因而较低,而且绝缘体可以减少存储单元之间的干扰,相对更容易实现微细化。 ※3D CTF结构 (3D Charge Trap Flash) 将传统的单层CTF结构改良升级为3D立体结构。原来长方形的控制栅被改为像戒指一样中空的圆柱体,因而可以最大化的利用空间,并使堆叠制程更加容易实现。 ※NAND闪存结构比较图

责任编辑:陈晨

|

焦点资讯

-

- 5G时代持续发力6400万像素主摄+90Hz显示屏vivo X30意外曝光

-

驱动中国2019年11月6日消息 前不久,市场调研机构数据表明第三季度国内5G手机市场发货量vivo品牌以54.3%市场占有率名列前茅,iQOO Pro 5G版、vivo NEX3等5G机型在市......

-

- 三星Note 7很惊艳?看完这五点你可能要失望了

-

最近几天,随着三星Note 7发布,网络上一片赞歌,不论是媒体还是消费者对于这款安卓机皇不吝溢美之词。确实,这款手机不论是在做工还是在设计上,都代表了目前安卓手机的最......

-

- 你想要了解的都有!三星Note 7发布前最全汇总

-

目前,三星官方已经放出了Note 7发布会直播页面,看来三星对于这款手机也是相当的重视,在三星手机全球市场份额下滑,尤其是在中国市场中面临着来自国产手机严峻挑战的时候......

-

- 售价惊人!全球首款带夜视相机智能手机诞生,可录4K视频

-

丹麦科技公司Lumigon发布了全球首款带红外夜视相机的智能手机:Lumigon T3。事实上,关注手机行业的消费者应该都知道,这款手机其实是2012年发布的T2继任者。...

-

- FBI通过第三方破解iPhone 苹果还安全吗?

-

关于苹果与FBI之间的矛盾已经持续了好几个月,正当大家都在猜测,双方之间的矛盾还会进一步激化时,事情来了个一百八十度的大转弯!FBI竟然撤诉了,原因是已经破解了枪击案......